Getting started with GateMate FPGA

Hello everyone this is my first blog post in quite some time now so I have been a bit rusty.

I have got my self GateMate FPGA this time and we will see in the log how to get started with it.

The GateMateA1-EVB one of the few dev-board based on the GateMate CCGM1A1 FPGA and it packs quite a lot of features and connectors as well .

Like its VGA and PS2 keyboard connector.

Now our task in this log is to setup the required EDA tool chain for the board and say hello world (blink an led). We will be using the OSS CAD tool chain as that is suggested by the company.

Few assumption made in this log

- You are using linux ( Its ubuntu for me)

- You how to navigate in linux thought terminal.

- Maybe you have programmed an FPGA before.

With that said lets get started the step zero is to get the tool chain. For that we would refer to the OSS-CAD’s Github and download latest release.

Now using the unzip tool of your choice unzip the tool chain in your preferred destination. I prefer to use this .

| |

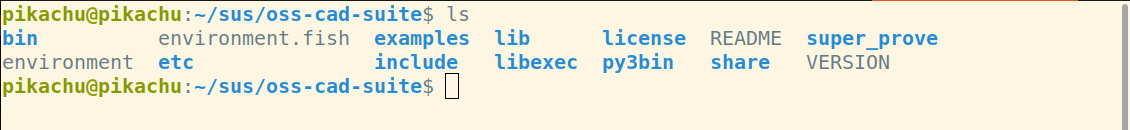

Now transition to the newly created oss-cad-suite directory you should have these files.

Now we need to export the path for the system to be able use the tool chain

| |

** Remember you would have to export this path every-time you open a new terminal . To solve you can add this your bashrc or set a alias for this .

Now to verify if you have everything correctly try running

| |

you should see a corresponding version number.

I will assume that you have got this shorted out should ideally work however use internet or chatgpt to solve if issues occur.

Ok onces the we got the tool-chain set-ed up .. to blink the led we need these files.

- Verilog (.v) file

- Pin Constraints (.ccf) file

For blinking a led the verilog looks rather simple

| |

To create a pin constraint file we would need to know the pin number corresponding to the led and clock pin on the board while there isnt a direct list of those available on olimex website however doing some digging we can take them from the schematic provided by the olimex .

We can see from this schematic that

- LED pin is IO_SB_B6

- CLk pin is IO_SB_A8

(note that these will differ for other dev kits based on same FPGA)

We will use these and create our constraint file blink.ccf

| |

Perfect now we have got all the files and tools we need it time to blink the led.

These are the steps we will follow.

- Synthesis

- PNR

- Bitstream Generation

- flash(programme) the fpga

1. Synthesis

The OSS-CAD is a yosys project thus it uses yosys for synthesis :>

We need to run this command for synthesis

| |

In our case the command will be

| |

This flow generate’s two files blinky.json and blinky_netlist.v in your directory now we will use those to do place and route.

2. Placement and Routing (PNR)

For pnr OSS-CAD use’s next-pnr and specifically we will use nextpnr-himbaechel which has the gatemate arch support.

The PNR requires these two files

- Netlist (.json) file

- Constraints (.ccf) file

which we already have and the command to run pnr is

| |

thus in our case this will become

| |

at the end of pnr we will get a blinky.txt that we will now use to pack the bitstream.

3. Bitstream Generation

To generate bitstream for GateMate fpga we have to use gmpack tool and its straight forward.

This is the command to use it

| |

Since we don’t need spi mode (Olimex board usage jtag) and crc and background reconfiguration for us it will be

| |

this will create a bitstream file by name blinky.bit now next step will be to upload this file to the board.

4. Flashing the FPGA

It time to take out the board out of the box and connect it to the laptop using the type C port on board.

For flashing the FPGA we will use openFPGALoader we have to use this command

| |

thus in our case this becomes

| |

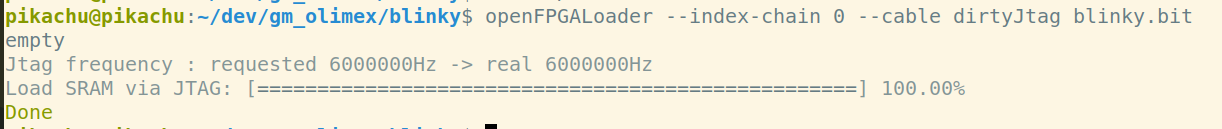

You should see something like this in the terminal

Congratulations we have the LED blinking on the board

Note: some times the openFPGALoader might not have correct usb access to read write you can provide the correct acess if that ocurs (consult google/chatgpt for solution)

I have uploaded the complete code and a make file for the tool chain on my gihub here along with other examples. If you have any questions you can raise issue in that repo.

Useful Links

Thank You For Reading

With Love

Deepak Sharda